# IDEC Chip Design Contest

## A Reconfigurable Ultrasonic Pulser-Reciever Circuit for a **Transducer with Large Capacitive Load**

Hyun-Tae Park<sup>1</sup>, and Ji-Yong Um<sup>1,2</sup> <sup>1</sup>Department of Electrical and Electronic Engineering, Hannam University <sup>2</sup>Department of Medical IT Convergence Engineering, Kumoh National Institute of Technology

### Introduction

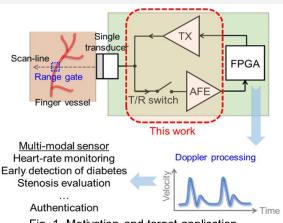

Fig. 1. Motivation and target application

- Target application

- Ultrasonic sensor module with single transducer

- Focus of this work

- Transducer interface circuit with reconfigurable topology

- Primary requirements and countermeasures

| • •                                                         |                                                        |  |

|-------------------------------------------------------------|--------------------------------------------------------|--|

| Requirement                                                 | Countermeasure                                         |  |

| Large capacitive load (few nF)<br>Center freq. up to 10 MHz | Minimum transistor stack in<br>High-voltage pulser     |  |

| Small active area                                           | Reconfigurable topology including pulse and T/R switch |  |

| Low noise performance of preamplifier                       | Optimization of operational region of transistors      |  |

## Schematic Diagram

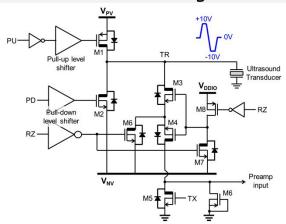

Fig. 2. Schematic of high-voltage pulser with T/R switch

- Reconfigurable high-voltage pulser with T/R switch

- Bipolar/Unipolar pulsing with 5V/3.3V logic control

- GND-path HV switch reconfigured as T/R switch

#### Measurements

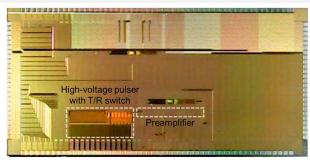

Fig. 3. Chip micrograph

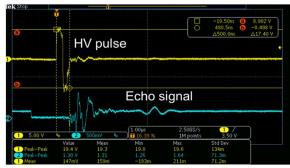

Fig. 4. Measured waveforms

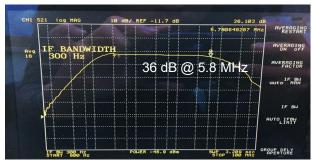

Fig. 5. Measured frequency response of preamplifier

## **Summary**

|                        | This work            | JSSC'20               | JSSC'13             |

|------------------------|----------------------|-----------------------|---------------------|

| Process                | 180nm BCD            | 180nm BCD             | 180nm HV CMOS       |

| Max output             | 20 Vpp               | 60 Vpp                | 30 Vpp              |

| Max. carrier frequency | 11 MHz               | 9 MHz                 | 3.3 MHz             |

| Load cap               | 5 nF                 | 18 pF                 | 40 pF               |

| T/R<br>embedded        | Yes                  | Yes                   | No                  |

| Active area            | 0.31 mm <sup>2</sup> | 0.167 mm <sup>2</sup> | $0.33 \text{ mm}^2$ |

#### Acknowledgement

This work was supported by Basic Science Research Program through the National Research Foundation (NRF) of Korea funded by the Ministry of Education (2019R1I1A3A01060591), and chip fabrication along with EDA tools were supported by the IC Design Education Center (IDEC) of Korea.